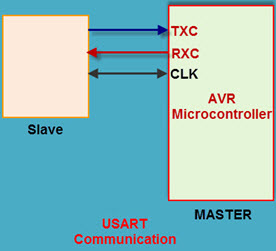

;********************************************** ;3/1/2019 ;Transmitts strings of characters from uP to PC ;********************************************** .include "ATxmega128A1Udef.inc" .dseg .org 0x2000 Outs: .BYTE 3 .cseg .org 0x0000 rjmp Main Main: ldi YL, low(Outs) ;input ldi YH, high(Outs) ldi XL, low(Outs) ;output ldi XH, high(Outs) ldi r16, 0xFF ;echo test sts PORTC_DIR, r16 sts PORTC_OUT, r16 rcall USART_INIT ;setup USART rcall IN_STRING rcall OUT_STRING LOOP: rjmp LOOP ;****************************************** ;This subroutine initializes the USART ;frame = 8 stop = 1 parity = odd ;baud = 115200 USART = PORT D ;****************************************** USART_INIT: push r16 ;push reg used ldi r16, 0x08 ;Rx out, rest in sts PORTD_DIRSET, r16 ldi r16, 0x18 ;Tx and Rx enables sts USARTD0_CTRLB, r16 ldi r16, 0x33 ;00 - async, 11 - odd sts USARTD0_CTRLC, r16 ;0 - ...